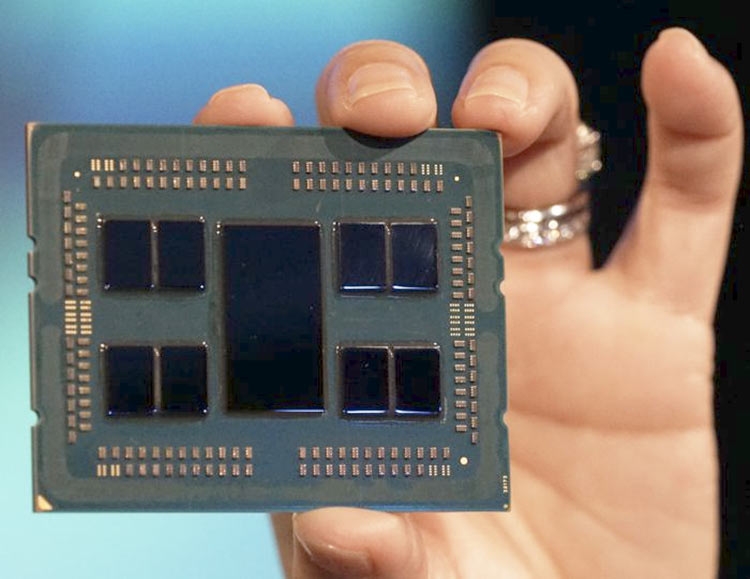

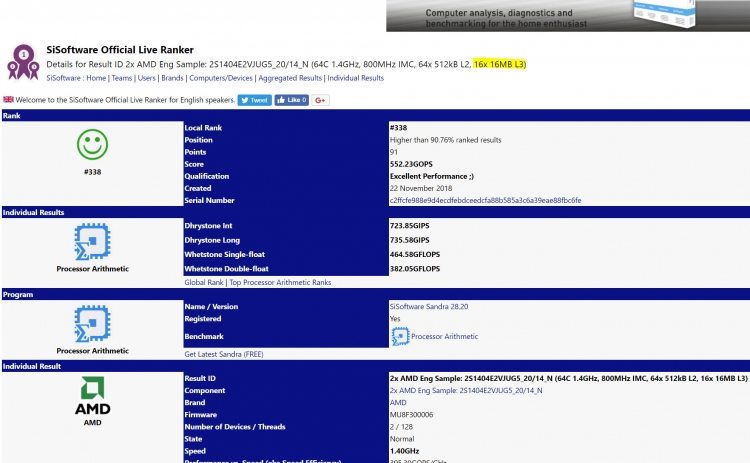

Выявленная в информационной базе испытательного пакета SiSoftware Sandy запись, касающаяся двухпроцессорной системы на основе серверного микропроцессора AMD EPYC рода Rome, проливает свет на иерархию кеш-памяти этого чипсета. Напоминаем: любой 64-ядерный микропроцессор EPYC Rome состоит из 8 7-нм 8-ядерных чипов («чиплетов») с архитектурой Zen 2, которые соединены 14-нм контроллером ввода-вывода (модуль I/O), отвечающим за работу с памятью, зависимость между чиплетами и PCIe-соединения.

В итоге тестирования упоминается следующая иерархия кеш-памяти: выделенный кеш L2 объёбог 512 Кб на любое ядро ??и 16 по 16 Мбайт кеша L3. Как и CPU-Z, Sandy может показывать расположение кеш-памяти L3. Для микропроцессора Ryzen 7 2700X пакет рассказывает, что кеш-память L3 распределена по принципу 2 x 8 Мбайт, что отвечает совместному кешу L3 объёбог по 8 Мбайт на любой 4-ядерный блок CCX.

В любом 64-ядерном микропроцессоре Rome присутствует суммарно 8 чиплетов. Если Sandy правильно рассказывает расположение кеша L3, то, по-видимому, любой из этих 8-ядерных кристаллов как и прежде разделён на 2 четырёхъядерных блока CCX. К тому же 1 CCX приобретает 16 Мбайт совместного кеша L3.

Это дублирование объёма буферной памяти L3 на любом CCX, возможно, призвано несколько возмещать неприятности, вызываемые задержками при передаче данных между 8-ядерными чиплетами и кристаллом ввода/вывода в свежих серверных микропроцессорах EPYC. Это в особенности принципиально, так как 8-канальный контроллер памяти DDR4 находится как раз на данном 14-нм кристалле.

Июль 26th, 2023

Июль 26th, 2023  raven000

raven000  Опубликовано в рубрике

Опубликовано в рубрике