Организация SK Hynix — 2-й во всем мире по величине изготовитель памяти вида DRAM — рассказала о подготовке 16-Гбит кристаллов DRAM DDR5 с применением 2-го поколения техпроцесса класса 10 hm (1Ynm). Есть тот же самый новый процесс компании, при помощи которого она начинает изготовление 8-Гбит кристаллов DDR4. Забегая вперёд, стоит отметить, что к изготовлению памяти DDR5 организация SK Hynix приступит в 2020 году, так как этот эталон DRAM пока ещё не принят советом JEDEC и не удерживается создателями контроллеров и микропроцессоров. Это только болванка на будущее, которая ждёт собственного дня.

По сценарию специалистов компании IDC, к примеру, спрос на DDR5 начнёт возникать в 2020 году, что гарантирует привести в 2021 году долю DDR5 во всемирном объёме изготовления памяти до 25 % и до 44 % в 2022 году. Потому компании SK Hynix, как и другим руководителям рынка DRAM, не надо торопиться с внедрением в изготовление этого поколения памяти. А начнётся всё с покорения серверного рынка, для которого DDR5 преподнесёт вероятность увеличить банки памяти и повысить скорость передачи данных от модулей к микропроцессорам и назад.

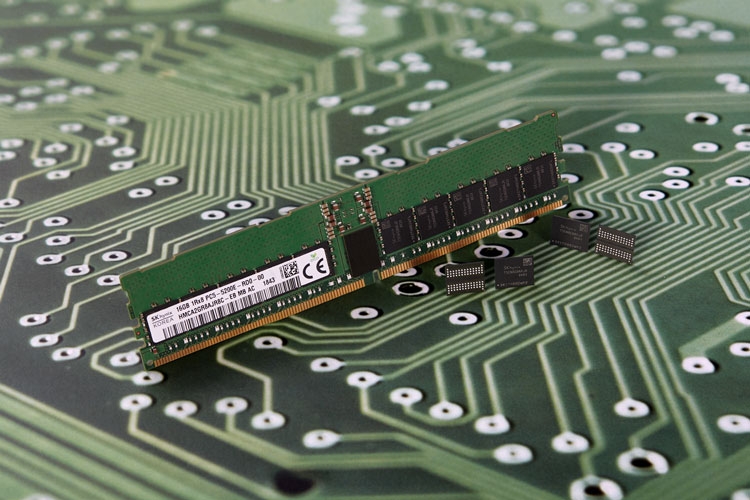

По условиям грязный редакции стереотипа DDR5, питание чипов понижено с 1,2 В до 1,1 В, что гарантирует понизить употребление памяти на 30 % сравнивая с памятью DDR4. При этом скорость размена повысилась на 60 % либо до 5200 Mbit/с, если приравнивать с одной из быстрейших сегодня памятью DDR4-3200. Совместно скорость размена с модулем памяти DDR5 увеличится до 41,6 Гигабайт/с — это 11 кинофильмов с качеством Full HD, представленных за 1 сек, любой из которых будет «весить» 3,7 Гигабайт. По традиции пустой образец, да, а даёт представление о размерах перемен. Настолько мгновенная память, убеждены в компании, даст свежий импульс формированию платформ ИИ, автомобильного учебы и работам с массивами данных.

Для понижения погрешностей чтения создателям понадобилось привнести очень много перемен в схемотехнику памяти. К слову, контрольные внешние виды понадобилось подвергнуть доработке также потому, что модули памяти DDR5 будут применять в два раза больше банков (32 вместо 16), чем память DDR4. Это также попросило вести слаженные работы с изготовителями модулей RDIMM (Registered Dual In-line Memory Module) и UDIMM (Unbuffered DIMM) для серверных платформ. Также организация утверждает, что механизмы корректировки ECC отныне интегрированы в чипсеты памяти. Всё надёжнее и надёжнее, что обусловлено также ускорением размена.

Декабрь 29th, 2023

Декабрь 29th, 2023  raven000

raven000  Опубликовано в рубрике

Опубликовано в рубрике